L’architecture des ordinateurs est conforme à un schéma qui a peu évolué depuis son origine en 1945 : le modèle dit de von Neumann.

I. L’architecture de von Neumann

1) Les structures principales

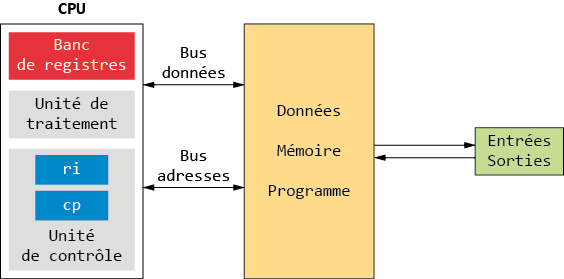

Dans l’architecture de von Neumann, un ordinateur est constitué de quatre parties distinctes :

- le CPU (Central Processing Unit ou unité centrale de traitement), plus communément appelée le processeur ;

- la mémoire où sont stockés les données et les programmes ;

- des bus qui sont en fait des fils conduisant des impulsions électriques et qui relient les différents composants ;

- des entrées-sorties (E/S ou I/O input/output) pour échanger avec l’extérieur.

2) Les sous-structures

Les échanges entre la mémoire et les registres du CPU se font via des bus selon une chronologie organisée par l’horloge et suivant la nature des échanges (données ou adresses).

Un programme est enregistré dans la mémoire.

L’adresse (un nombre entier) de l’instruction en cours de traitement est stockée dans une mémoire interne au processeur nommée « registre compteur de programme » (cp ou pc).

La valeur de cette instruction (un entier) est stockée dans une autre mémoire interne : le « registre d’instruction » (ri).

Le CPU dispose aussi de mémoires internes dans le « banc de registres » où sont placées les données du programme avant utilisation.

L’UAL ou ALU (unité arithmétique et logique) effectue les opérations arithmétiques et logiques, sur les données et les adresses, en interprétant les impulsions électriques sortant de ses circuits combinatoires fabriqués à l’aide de circuits élémentaires (NAND en particulier).

II. Le rôle de l’horloge

1) Cadence d’un processeur

Le CPU dispose d’une horloge qui cadence l’accomplissement des instructions. L’unité est appelée cycle.

Lorsqu’on parle d’un processeur cadencé à 3 GHz, cela signifie qu’il y a 3 milliards de cycles d’horloge par seconde. Jusqu’en 2004 environ, la fréquence des processeurs a augmenté linéairement. Depuis, elle stagne. En effet, au-delà, la chaleur produite devient trop importante et pourrait perturber la lecture des tensions lues aux bornes des circuits de l’UAL voire détériorer physiquement ses circuits.

2) Cycle d’instructions

Dans une machine de Turing, un cycle représente l’ensemble des quatre actions : lire, écrire, changer d’état, se déplacer.

À noter

Voir une machine de Turing cadencée à 0,5 Hz en action : https://youtu.be/VpDMAVKWvb4).

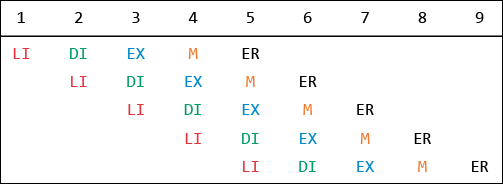

Dans un processeur, ce que l’on appelle cycle est un peu différent. En effet, chacune des cinq actions suivantes est exécutée lors d’un cycle : lire l’instruction (LI), décoder l’instruction (DI), exécuter l’opération dans l’UAL (EX), accéder à la mémoire en lecture ou en écriture (M), écrire le résultat dans les registres (ER).

Pour gagner du temps, le processeur n’exécute pas les instructions de manière séquentielle mais exécute simultanément plusieurs instructions qui sont à des étapes différentes de leur traitement. C’est le principe du « pipeline d’instructions »

Exemple : Dans la figure ci-dessous, on a 5 instructions qui devraient demander 25 cycles pour être exécutées. Ici, il en faut seulement 9. Cette optimisation peut être freinée par des branchements ou accélérée par une meilleure organisation de la mémoire.